NOTICE OF CHANGE

INCH-POUND

The documentation and process conversion measures necessary to comply with this notice shall be completed by 5 January 2003.

MIL-STD-750D NOTICE 5 12 November 2002

### DEPARTMENT OF DEFENSE

# TEST METHOD STANDARD FOR SEMICONDUCTOR DEVICES

TO ALL HOLDERS OF MIL-STD-750D:

1. THE FOLLOWING PAGES OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE PAGES LISTED:

| NEW PAGE | DATE             | SUPERSEDED PAGE | DATE          |

|----------|------------------|-----------------|---------------|

| 15       | 12 November 2002 | 15              | 30 April 2001 |

| 16       | 12 November 2002 | 16              | 30 April 2001 |

| 17       | 12 November 2002 | 17              | 30 April 2001 |

| 18       | 12 November 2002 | 18              | 30 April 2001 |

| 19/20    | 12 November 2002 | 19/20           | 30 April 2001 |

2. THE FOLLOWING TEST METHODS OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE TEST METHOD LISTED:

| METHOD | DATE             | SUPERSEDED METHOD | DATE             |

|--------|------------------|-------------------|------------------|

| 1018.2 | 12 November 2002 | 1018.1            | 30 April 2001    |

| 2071.6 | 12 November 2002 | 2071.5            | 30 April 2001    |

| 2074.4 | 12 November 2002 | 2074.3            | 23 February 1996 |

| 3131.4 | 12 November 2002 | 3131.3            | 30 April 2001    |

| 3306.4 | 12 November 2002 | 3306.3            | 28 February 1995 |

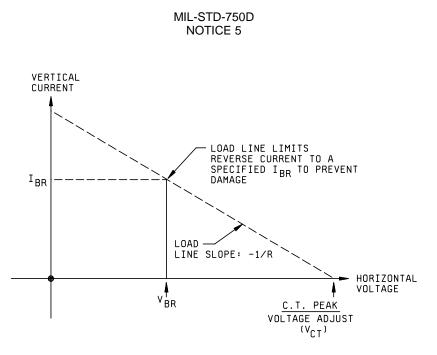

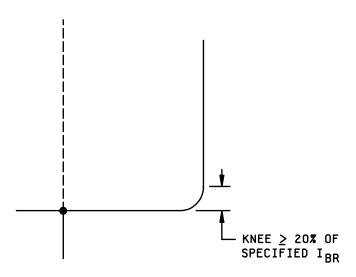

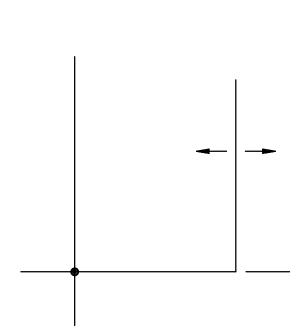

| 4023.1 | 12 November 2002 | 4023              | 28 February 1995 |

3. THE FOLLOWING NEW METHODS HAVE BEEN ADDED:

| METHOD | TITLE                            | DATE             |

|--------|----------------------------------|------------------|

| 1057   | Resistance to glass cracking     | 12 November 2002 |

| 3100   | Junction temperature measurement | 12 November 2002 |

4. RETAIN THIS NOTICE AND INSERT BEFORE TABLE OF CONTENTS.

5. Holders of MIL-STD-750D will verify that page changes and additions indicated above have been entered. This notice page will be retained as a check sheet. This issuance, together with appended pages, is a separate publication. Each notice is to be retained by stocking points until the military standard is completely revised or canceled.

NOTE: The margins of this notice are marked with asterisks to indicate where changes from the previous issue were made. This was done as a convenience only and the Government assumes no liability whatsoever for any inaccuracies in these notations. Bidders and contractors are cautioned to evaluate the requirements of this document based on the entire content irrespective of the marginal notations and relationship to the last previous issue.

Custodians: Army - CR Navy - EC Air Force - 11 NASA – NA DLA-CC Preparing activity: DLA - CC

(Project 5961-2661)

Review activities: Army - AR, MI Navy - AS, MC, SH Air Force – 19, 99

#### NUMERICAL INDEX OF TEST METHODS

| METHOD NO. | TITLE |

|------------|-------|

|            |       |

Environmental tests (1000 series).

- 1001.2 Barometric pressure (reduced).

- 1011.1 Immersion.

- 1015.1 Steady-state primary photocurrent irradiation procedure (electron beam).

- 1016 Insulation resistance.

- 1017.1 Neutron irradiation.

- 1018.2 Internal gas analysis

- 1019.4 Steady-state total dose irradiation procedure.

- 1020.2 Electrostatic discharge sensitivity (ESDS) classification.

- 1021.3 Moisture resistance.

- 1022.5 Resistance to solvents.

- 1026.5 Steady-state operation life.

- 1027.3 Steady-state operation life (sample plan).

- 1031.5 High-temperature life (nonoperating).

- 1032.2 High-temperature (nonoperating) life (sample plan).

- 1033 Reverse Voltage Leakage Stability

- 1036.3 Intermittent operation life.

- 1037.2 Intermittent operation life (sample plan).

- 1038.4 Burn-in (for diodes, rectifiers, and zeners).

- 1039.4 Burn-in (for transistors).

- 1040 Burn-in (for thyristors (controlled rectifiers)).

- 1041.3 Salt atmosphere (corrosion).

- 1042.3 Burn-in and life test for power MOSFET's or insulated gate bipolar transistors (IGBT).

- 1046.3 Salt spray (corrosion).

- 1048 Blocking life.

- 1049 Blocking life (sample plan).

- 1051.7 Temperature cycling (air to air).

- 1054.1 Potted environment stress test.

- 1055.1 Monitored mission temperature cycle.

- 1056.7 Thermal shock (liquid to liquid).

- 1057 Resistance to glass cracking

- 1061.1 Temperature measurement, case and stud.

- 1066.1 Dew point.

- 1071.7 Hermetic seal

- 1080 Single Event Gate Rupture and Drain Burnout Test

# Mechanical characteristics tests (2000 series).

- 2005.2 Axial lead tensile test.

- 2006 Constant acceleration.

- 2016.2 Shock.

- 2017.2 Die attach integrity.

- 2026.10 Solderability.

- 2031.2 Soldering heat.

- 2036.4 Terminal strength.

- 2037.2 Bond strength.

- 2046.1 Vibration fatigue.

- 2051.1 Vibration noise.

- 2052.3 Particle impact noise detection (PIND) test.

SUPERSEDES PAGE 15 OF NOTICE 4 TO MIL-STD-750D.

#### NUMERICAL INDEX OF TEST METHODS - Continued.

METHOD NO. TITLE

### Mechanical characteristics tests (2000 series) - Continued.

- 2056 Vibration, variable frequency.

- 2057.1 Vibration, variable frequency (monitored).

- 2066 Physical dimensions.

- 2068 External visual for nontransparent, glass-encased, double plug, noncavity, axial leaded diodes.

- 2069.2 Pre-cap visual, power MOSFET's.

- 2070.2 Pre-cap visual microwave discrete and multichip transistors.

- 2071.6 Visual and mechanical examination.

- 2072.6 Internal visual transistor (pre-cap) inspection.

- 2073.1 Internal inspection for die (semiconductor diode).

- 2074.4 Internal visual inspection (discrete semiconductor diodes).

- 2075.1 Decap internal visual design verification.

- 2076.3 Radiography.

- 2077.3 Scanning electron microscope (SEM) inspection of metallization.

- 2081 Forward instability, shock (FIST).

- 2082 Backward instability, vibration (BIST).

- 2101.1 DPA procedures for diodes.

- 2102 DPA for wire bonded devices

Electrical characteristics tests for bipolar transistors (3000 series).

- 3001.1 Breakdown voltage, collector to base.

- 3005.1 Burnout by pulsing.

- 3011.2 Breakdown voltage, collector to emitter.

- 3015 Drift.

- 3020 Floating potential.

- 3026.1 Breakdown voltage, emitter to base.

- 3030 Collector to emitter voltage.

- 3036.1 Collector to base cutoff current.

- 3041.1 Collector to emitter cutoff current.

- 3051 Safe operating area (continuous dc).

- 3052 Safe operating area (pulsed).

- 3053 Safe operating area (switching).

- 3061.1 Emitter to base cutoff current.

- 3066.1 Base emitter voltage (saturated or nonsaturated).

- 3071 Saturation voltage and resistance.

- 3076.1 Forward-current transfer ratio.

- 3086.1 Static input resistance.

- 3092.1 Static transconductance.

Circuit-performance and thermal resistance measurements (3100 series).

- 3100 Junction temperature measurement

- 3101.3 Thermal impedance testing of diodes.

- 3103 Thermal impedance measurements for insulated gate bipolar transistor (delta gate-emitter on voltage method).

- 3104 Thermal impedance measurements of GaAs MOSFET's (constant current forward-biased gate voltage method).

- 3105.1 Measurement method for thermal resistance of a bridge rectifier assembly.

SUPERSEDES PAGE 16 OF NOTICE 4 TO MIL-STD-750D.

#### NUMERICAL INDEX OF TEST METHODS - Continued.

METHOD NO. TITLE

Circuit-performance and thermal resistance measurements (3100 series) - Continued.

3126 Thermal resistance (collector-cutoff-current method).

- 3131.4 Thermal impedance measurements for bipolar transistors (delta base-emitter voltage method).

- 3132 Thermal resistance (dc forward voltage drop, emitter base, continuous method).

- 3136 Thermal resistance (forward voltage drop, collector to base, diode method).

- 3141 Thermal response time.

- 3146.1 Thermal time constant.

- 3151 Thermal resistance, general.

- 3161 Thermal impedance measurements for vertical power MOSFET's (delta source-drain voltage method).

- 3181 Thermal resistance for thyristors.

Low frequency tests (3200 series).

- 3201.1 Small-signal short-circuit input impedance.

- 3206.1 Small-signal short-circuit forward-current transfer ratio.

- 3211 Small-signal open-circuit reverse-voltage transfer ratio.

- 3216 Small-signal open-circuit output admittance.

- 3221 Small-signal short-circuit input admittance.

- 3231 Small-signal short-circuit output admittance.

- 3236 Open circuit output capacitance.

- 3240.1 Input capacitance (output open-circuited or short-circuited).

- 3241 Direct interterminal capacitance.

- 3246.1 Noise figure.

- 3251.1 Pulse response.

- 3255 Large signal power gain.

- 3256 Small signal power gain.

- 3261.1 Extrapolated unity gain frequency.

- 3266 Real part of small-signal short circuit input impedance.

High frequency tests (3300 series)

- 3301 Small-signal short-circuit forward-current transfer-ratio cutoff frequency.

- 3306.4 Small-signal short-circuit forward-current transfer ratio.

- 3311 Maximum frequency of oscillation.

- 3320 RF power output, RF power gain, and collector efficiency.

Electrical characteristics tests for MOS field-effect transistors (3400 series)

- 3401.1 Breakdown voltage, gate to source.

- 3403.1 Gate to source voltage or current.

- 3404 MOSFET threshold voltage.

- 3405.1 Drain to source on-state voltage.

- 3407.1 Breakdown voltage, drain to source.

- 3411.1 Gate reverse current.

- 3413.1 Drain current.

- 3415.1 Drain reverse current.

- 3421.1 Static drain to source on-state resistance.

- 3423 Small-signal, drain to source on state resistance.

- 3431 Small-signal, common-source, short-circuit, input capacitance.

- 3433 Small-signal, common-source, short-circuit, reverse-transfer capacitance.

SUPERSEDES PAGE 17 OF NOTICE 4 TO MIL-STD-750D.

### NUMERICAL INDEX OF TEST METHODS - Continued.

METHOD NO. TITLE Electrical characteristics tests for MOS field-effect transistors (3400 series) - Continued. Small-signal, common-source, short-circuit, output admittance. 3453 3455 Small-signal, common-source, short-circuit, forward transadmittance. 3457 Small-signal, common-source, short-circuit, reverse transfer admittance. 3459 Pulse response (FET). Small-signal, common-source, short-circuit, input admittance. 3461 3469 Repetitive unclamped inductive switching. 3470.2 Single pulse unclamped inductive switching. Gate charge. 3471.2 3472.2 Switching time test. 3473.1 Reverse recovery time (trr) and recovered charge (Qrr) for power MOSFET (drain-to-source) and power rectifiers with trr • 100 ns. Safe operating area for power MOSFET's or insulated gate bipolar transistors. 3474.1 3475.1 Forward transconductance (pulsed dc method) of power MOSFET's or insulated gate bipolar transistors. 3476 Commutating diode for safe operating area test procedure for measuring dv/dt during reverse recovery of power MOSFET transistors or insulated gate bipolar transistors. 3477.1 Measurement of insulated gate bipolar transistor total switching losses and switching times. Power transistor electrical dose rate test method. 3478.1 3479 Short circuit withstand time. 3490 Clamped inductive switching safe operating area for MOS gated power transistors. Electrical characteristics tests for Gallium Arsenide transistors (3500 series) Breakdown voltage, drain to source. 3501 3505 Maximum available gain of a GaAs FET. 1 dB compression point of a GaAs FET. 3510 3570 GaAs FET forward gain (Mag S21).

- 3570 GaAS FET IOI ward gain (Wag 52

- 3575 Forward transconductance.

Electrical characteristics tests for diodes (4000 series).

- 4000 Condition for measurement of diode static parameters.

- 4001.1 Capacitance.

- 4011.4 Forward voltage.

- 4016.4 Reverse current leakage.

- 4021.2 Breakdown voltage (diodes).

- 4022 Breakdown voltage (voltage regulators and voltage-reference diodes).

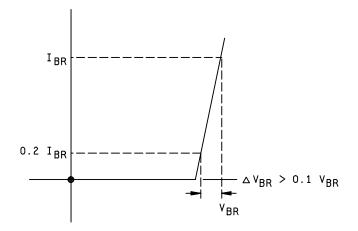

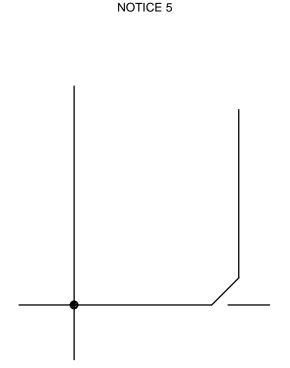

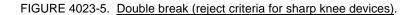

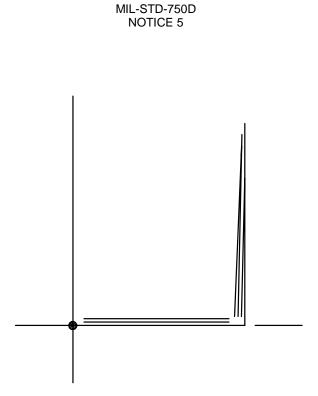

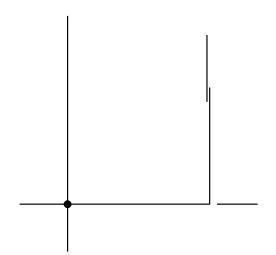

- 4023.1 Scope display.

- 4026.3 Forward recovery voltage and time.

- 4031.4 Reverse recovery characteristics.

- 4036.1 "Q" for voltage variable capacitance diodes.

- 4041.2 Rectification efficiency.

- 4046.1 Reverse current, average.

- 4051.3 Small-signal reverse breakdown impedance.

- 4056.2 Small-signal forward impedance.

- 4061.1 Stored charge.

SUPERSEDES PAGE 18 OF NOTICE 4 TO MIL-STD-750D.

#### NUMERICAL INDEX OF TEST METHODS - Continued.

METHOD NO. TITLE

# Electrical characteristics tests for diodes (4000 series) - Continued.

- 4066.4 Surge current.

- 4071.1 Temperature coefficient of breakdown voltage.

- 4076.1 Saturation current.

- 4081.2 Thermal resistance of lead mounted diodes (forward voltage, switching method).

### Electrical characteristics tests for microwave diodes (4100 series)

- 4101.3 Conversion loss.

- 4102 Microwave diode capacitance.

- 4106 Detector power efficiency.

- 4111.1 Figure of merit (current sensitivity).

- 4116.1 IF impedance.

- 4121.2 Output noise ratio.

- 4126.2 Overall noise figure and noise figure of the IF amplifier.

- 4131.1 Video resistance.

- 4136.1 Standing wave ratio (SWR).

- 4141.1 Burnout by repetitive pulsing.

- 4146.1 Burnout by single pulse.

- 4151 Rectified microwave diode current.

#### Electrical characteristics tests for tunnel diodes (4300 series)

- 4301 Junction capacitance.

- 4306.1 Static characteristics of tunnel diodes.

- 4316 Series inductance.

- 4321 Negative resistance.

- 4326 Series resistance.

- 4331 Switching time.

### High reliability space application tests (5000 series)

- 5001.2 Wafer lot acceptance testing.

- 5002 Capacitance-voltage measurements to determine oxide quality.

- 5010 Clean room and workstation airborne particle classification and measurement.

SUPERSEDES PAGE 19/20 OF NOTICE 4 TO MIL-STD-750D.

#### METHOD 1018.2

#### **INTERNAL GAS ANALYSIS**

1. <u>Purpose</u>. The purpose of this test is to measure the water-vapor content of the atmosphere inside a metal or ceramic hermetically-sealed device. It can be destructive (procedures 1 and 2) or nondestructive (procedure 3).

2. <u>Apparatus</u>. The apparatus for the internal water-vapor content test shall be as follows for the chosen procedure:

2.1 <u>Procedure 1</u>. (Procedure 1 measures the water-vapor content of the device atmosphere by mass spectrometry.) The apparatus for procedure 1 shall consist of:

- a. A mass spectrometer meeting the following requirements:

- (1) Spectra range. The mass spectrometer shall be capable of reading a minimum spectra range of 1 to 100 atomic mass units (AMUs).

- (2) Detection limit. The mass spectrometer shall be capable of reproducibly detecting the specified moisture content for a given volume package with signal to noise ratio of 20 to 1 (i.e., for a specified limit of 5,000 parts per million volume (ppmv), .01 cc, the mass spectrometer shall demonstrate a 250 ppmv minimum detection limit to moisture for a package volume of .01 cc). The smallest volume shall be considered the worst case.

- (3) Calibration. The calibration of the mass spectrometer shall be accomplished at the specified moisture limit (±20 percent) using a package simulator which has the capability of generating at least three known volumes of gas ±10 percent on a repetitive basis by means of a continuous sample volume purge of known moisture content ±10 percent. Moisture content shall be established by the standard generation techniques (i.e., 2 pressure, divided flow, or cryogenic method). The dew point analyzer shall be recalibrated a minimum of once per year using equipment traceable to NIST or by a suitable commercial calibration services laboratory using equipment traceable to NIST standards. Calibration records shall be kept on a daily basis. Gas analysis results obtained by this method shall be considered valid only in the moisture range or limit bracketed by at least two (volume or concentration) calibration points (i.e., 5,000 ppmv between .01 .1 cc or 1,000 5,000 ppmv between .01 .1 cc). A best fit curve shall be used between volume calibration points. Systems not capable of bracketing may use an equivalent procedure as approved by the qualifying activity. Corrections of sensitivity factors deviating greater than 10 percent from the mean between calibration points shall be required.

NOTE: It is recommended that the percentage of water vapor contained in a gas flowing through the gas humidifier be compared to the dewpoint sensor reading for accuracy of the sensor. The following equation may be used to calculate the percent of water vapor contained in a gas flowing through the gas humidifier.

$$\% H 2O = \frac{100 (Pv \, mb)}{68.95 \, mb/psi Pg + 1.33 \, mb/mm Pa}$$

Where:

$P_v$  = vapor pressure of water in the GPH based on water temperature in degrees centigrade,

$P_g = gauge pressure in psi, and$

$P_a$  = atmospheric pressure in mm Hg.

- \*(4) Calibration for other gases. Calibration shall be required for all gases found in concentrations greater than .01 percent by volume. As a minimum, this shall include all gases listed in 3.1c. The applicable gases shall be calibrated at approximately 1 percent concentrations as part of the yearly calibration requirements, with the exception of fluorocarbons, which may use a concentration of approximately 200 ppmv; nitrogen, which may use a concentration of approximately 80 percent; helium, which may use a concentration of approximately 10 percent; and oxygen, which may use a concentration of approximately 20 percent.

- (5) Calibration check. The system calibration shall be checked on the day of test prior to any testing. This shall include checking the calibration by in-letting a 5000 ppmv ±20 percent moisture calibration sample of the required volumes and comparing the result with the calibration sample. The resulting moisture reading shall be within 250 ppmv of the moisture level in the calibration sample. Calibration performed on the day of test prior to any testing may be substituted for this calibration check.

- b. A vacuum opening chamber which can contain the device and a vacuum transfer passage connecting the device to the mass spectrometer of 2.1a. The system shall be maintained at a stable temperature equal to or above the device temperature. The fixturing in the vacuum opening chamber shall position the specimen as required by the piercing arrangement of 2.1c, and maintain the device at 100°C ±5°C for a minimum of 10 minutes prior to piercing.

NOTE: A maximum 5 minute transfer time from prebake to hot insertion into apparatus shall be allowed. If 5 minutes is exceeded, device shall be returned to the prebake oven and prebake continued until device reaches  $100^{\circ}C \pm 5^{\circ}C$ .

For initial certification of systems or extension of suitability, device temperature on systems using an external fixture shall be characterized by placing a thermocouple into the cavity of a blank device of similar mass, internal volume, construction and size. This shall be a means for proving the device temperature has been maintained at  $100^{\circ}C \pm 5^{\circ}C$  for the minimum 10 minutes. This also applies to devices prebaked in an external oven but tested with the external fixture to adjust for any temperature drop during the transfer. These records shall be maintained by the test laboratory.

c. A piercing arrangement functioning within the opening chamber or transfer passage of 2.1b, which can pierce the specimen housing (without breaking the mass spectrometer chamber vacuum and without disturbing the package sealing medium), thus allowing the specimen's internal gases to escape into the chamber and mass spectrometer.

NOTE: A sharp-pointed piercing tool, actuated from outside the chamber wall via a bellows to permit movement, should be used to pierce both metal and ceramic packages. For ceramic packages, the package lid or cover should be locally thinned by abrasion to facilitate localized piercing.

2.2 <u>Procedure 2</u>. (Procedure 2 measures the water-vapor content of the device atmosphere by integrating moisture picked up by a dry carrier gas at 50°C.) The apparatus for procedure 2 shall consist of:

- a. An integrating electronic detector and moisture sensor capable of reproducibly detecting a water-vapor content of 300 ppmv ±50 ppmv moisture for the package volume being tested. This shall be determined by dividing the absolute sensitivity in micrograms H<sub>2</sub>0 by the computed weight of the gas in the device under test, and then correcting to ppmv.

- b. A piercing chamber or enclosure, connected to the integrating detector of 2.2a, which will contain the device specimen and maintain its temperature at 100°C ±5°C during measurements. The chamber shall position the specimen as required by the piercing arrangement. The piercing mechanism shall open the package in a manner which will allow the contained gas to be purged out by the carrier gas or removed by evacuation. The sensor and connection to the piercing chamber will be maintained at a temperature of 50°C ±2°C.

2.3 <u>Procedure 3</u>. (Procedure 3 measures the water-vapor content of the device atmosphere by measuring the response of a calibrated moisture sensor or an IC chip which is sealed within the device housing, with its electrical terminals available at the package exterior.) The apparatus for procedure 3 shall consist of one of the following:

- a. A moisture sensor element and readout instrument capable of detecting a water-vapor content of 300 ppmv ±50 ppmv while sensor is mounted inside a sealed device.

- b. Metallization runs on the device being tested isolated by back-biased diodes which when connected as part of a bridge network can detect 2,000 ppmv within the cavity. The chip shall be cooled in a manner such that the chip surface is the coolest surface in the cavity. The device shall be cooled below dew point and then heated to room temperature as one complete test cycle.

NOTE: Suitable types of sensors may include (among others) parallel or interdigitated metal stripes on an oxidized silicon chip, and porous anodized-aluminum structures with gold-surface electrodes.

Surface conductivity sensors may not be used in metal packages without external package wall insulation. When used, the sensor shall be the coolest surface in the cavity. It should be noted that some surface conductivity sensors require a higher ionic content than available in ultraclean CERDIP packages. In any case, correlation with mass spectrometer procedure 1 shall be established by clearly showing that the sensor reading can determine whether the cavity atmosphere has more or less than the specified moisture limit at 100°C.

3. <u>Procedure</u>. The internal water-vapor content test shall be conducted in accordance with the requirement of procedure 1, procedure 2, or procedure 3. All devices shall be prebaked for 16 to 24 hours at 100°C  $\pm$ 5°C prior to hot insertion into apparatus. External ovens shall have a means to indicate if a power interuption occurs during the prebaking period and for how long the temperature drops below 100°C  $\pm$  5°C. Devices baked in an external oven which loses power and whose temperature drops below 100°C  $\pm$  5°C for more than 1 hour shall undergo another prebake to begin a minimum of 12 hours later.

NOTE: It is recommended that samples submitted to the labs shall include information about the manufacturing process including sealing temperature, sealing pressure, sealing gas, free internal cavity volume, lid thickness at puncture site, lid material, and the location of the puncture site.

3.1 <u>Procedure 1</u>. The device shall be hermetic in accordance with test method 1071, and free from any surface contaminants which may interfere with accurate water-vapor content measurement.

After device insertion, the device and chamber shall be pumped down and baked out at a temperature of 100°C ±5°C until the background pressure level will not prevent achieving the specified measurement accuracy and sensitivity. After pumpdown, the device case or lid shall be punctured and the following properties of the released gases shall be measured, using the mass spectrometer:

- a. The increase in chamber pressure as the gases are released by piercing the device package. A pressure rise of less than 50 percent of normal for that package volume and pressurization may indicate that (1) the puncture was not fully accomplished, (2) the device package was not sealed hermetically, or (3) does not contain the normal internal pressure.

- b. The water-vapor content of the released gases, as a percent by unit volume or ppmv of the total gas content.

- c. The proportions (by volume) of the other following gases: N<sub>2</sub>, He, Mass 69 (fluorocarbons), O<sub>2</sub>, Ar, H<sub>2</sub>, CO<sub>2</sub>, CH<sub>4</sub>, NH<sub>3</sub>, and other solvents, if available. Calculations shall be made and reported on all gases present greater than .01 percent by volume. Data reduction shall be performed in a manner which will preclude the cracking pattern interference from other gas specie in the calculations of moisture content. Data shall be corrected for any system dependent matrix effects such as the presence of hydrogen in the internal ambient.

### 3.1.1 Failure criteria.

- a. A device which has a water-vapor content greater than the specified maximum value shall constitute a failure.

- b. A device which exhibits an abnormally low total gas content, as defined in 3.1a, shall constitute a failure, if it is not replaced. Such a device may be replaced by another device from the same population; if the replacement device exhibits normal total gas content for its type, neither it nor the original device shall constitute a failure for this cause.

3.2 <u>Procedure 2</u>. The device shall be hermetic in accordance with test method 1071, and free from any surface contaminants which may interfere with accurate water-vapor content measurement.

After device insertion into the piercing chamber, gas shall be flowed through the system until a stable base-line value of the detector output is attained. With the gas flow continuing, the device package shall then be pierced so that a portion of the purge gas flows through the package under test and the evolved moisture integrated until the base-line detector reading is again reached. An alternative allows the package gas to be transferred to a holding chamber which contains a moisture sensor and a pressure indicator. System is calibrated by injecting a known quantity of moisture or opening a package of known moisture content.

### 3.2.1 Failure criteria.

- a. A device which has a water-vapor content (by volume) greater than the specified maximum value shall constitute a failure.

- b. After removal from the piercing chamber, the device shall be inspected to ascertain that the package has been fully opened. A device package which was not pierced shall constitute a failure, if the test is not performed on another device from the same population; if this retest sample or replacement is demonstrated to be pierced and meets the specified water-vapor content criteria, the specimen shall be considered to have passed the test.

- c. A package which is a leaker in the purge case will be wet and counted as a failure. In the case of evacuation, a normal pressure rise shall be measured as in 3.1a.

3.3 <u>Procedure 3</u>. The moisture sensor shall be calibrated in an atmosphere of known water-vapor content, such as that established by a saturated solution of an appropriate salt or dilution flow stream. It shall be demonstrated that the sensor calibration can be verified after package seal or that post seal calibration of the sensor by lid removal is an acceptable procedure.

The moisture sensor shall be sealed in the device package or, when specified, in a dummy package of the same type. This sealing shall be done under the same processes, with the same die attach materials and in the same facilities during the same time period as the device population being tested.

The water-vapor content measurement shall be made, at 100°C or below, by measuring the moisture sensor response. Correlation with procedure 1 shall be accomplished before suitability of the sensor for procedure 3 is granted. It shall be shown the package ambient and sensor surface are free from any contaminating materials such as organic solvents which might result in a lower than usual moisture reading.

3.3.1 <u>Failure criteria</u>. A specimen which has a water-vapor content greater than the specified maximum value shall constitute a failure.

4. <u>Implementation</u>. Suitability for performing method 1018 analysis is granted by the qualifying activity for specific limits and volumes. Method 1018 calibration procedures and the suitability survey are designed to guarantee ±20 percent lab-to-lab correlation in making a determination whether the sample passes or fails the specified limit. Water vapor contents reported either above or below (water vapor content - volume) the range of suitability are not certified as correlatable values. This out of specification data has meaning only in a relative sense and only when one laboratory's results are being compared. The specification limit of 5,000 ppmv shall apply to all package volumes, with the following correction factors permitted, to be used provided they are documented and shown to be applicable:

For package volumes less than .01 cc internal free volume which are sealed while heated in a furnace:

$$C_T = \frac{T_r + 273}{T_r + 273}$$

For package volumes of any size sealed under vacuum conditions:

$$C_{P} = \frac{P_{s}}{P_{a}}$$

$C_P$  = correction factor (pressure)  $P_s$  = sealing pressure  $P_a$  = atmospheric pressure (pressures may be in Torr or mm Hg).

The correction factor, if used, shall be applied as follows:

Water vapor (corrected) = Water vapor (measured) x  $C_X$ ; where  $C_X$  is the applicable correction factor.

The range of suitability for each laboratory will be extended by the qualifying activity when the analytical laboratories demonstrate an expanded capability. Information on current analytical laboratory suitability status can be obtained by contacting Defense Supply Center, Columbus, ATTN: DSCC-VQE, P.O. Box 3990, Columbus, OH 43216-5000.

- 5. <u>Summary</u>. The following details shall be specified in the applicable acquisition document:

- a. The procedure (1, 2, or 3) when a specific procedure is to be used (see 3).

- b. The maximum allowable water-vapor content falling within the range of suitability as specified MIL-PRF-19500.

\* 6. <u>Surrogate monitors</u>. Surrogate monitors are only applicable for packages less than .01 cc to evaluate the process baseline. Surrogate monitors will be subject to RGA testing in accordance with method 1018 herein. A production lot will be validated by the performance of its monitors. It is well known and established that preseal bake and storage conditions of packaging materials will severely impact the levels of moisture detected in almost any package type. The use of the surrogate monitors without a controlled and disciplined manufacturing line is of questionable value. The proposed test is not, nor is it intended to be a direct measurement of small packaged product internal moisture. However, it is a quantifiable indicator that the process and controls used are consistent. This is an improvement over the existing situation in which there is a requirement for control of internal moisture and no accurate and repeatable method of measurement.

\* 6.1. <u>Requirements</u>. Surrogate monitors are to be procured from the same manufacturer and be manufactured in the same technology as the production headers, using the same materials, plating, processing and technology. For example, the UB packages: Kyocera header, multilayer cofired ceramic technology; SemiAlloys lid, Alloy 52, nickel underplate, gold plate.

- a. The device manufacturer shall use the same preconditioning on surrogate monitors and production product, i.e. vacuum bake time and temperature, storage conditions, die attach materials and process, etc.

- b. Surrogate monitors shall be sealed at the same time and using the same process as the production parts.

- c. To optimize the effect of preconditioning the transit time from the oven to the seal furnace shall be controlled and minimal.

- d. A typical process would include:

- (1) Batch high-vacuum bake headers and lids.

- (2) Store baked material in dry nitrogen.

- (3) Second vacuum bake overnight (min. 12 hrs) just prior to seal.

- (4) Minimize the post-2nd bake exposure to atmosphere.

- e. Surrogate monitor packages will be under baseline documentation control. Full traceability from procurement to utilization shall be maintained.

- f. Initially, the surrogate monitors will be used at the beginning of the seal operation and at 2 hour intervals. A minimum of six monitors must be processed for each seal lot (a "seal lot" may consist of multiple production lots if they go through sealing without interruptions (other than the scheduled breaks) and have identical traceability of headers and lids).

- g. It is expected that it will take approximately 6 months for a manufacturer to collect enough lots and data to establish a baseline. Later modifications of the preconditioning process will be evaluated against this baseline.

- h. The device manufacturer will submit to DSCC the results from a minimum of three "seal" lots to establish the effectiveness of the process baseline. Additional testing will be retained and available to DSCC upon request.

### METHOD 1057

# RESISTANCE TO GLASS CRACKING

1. <u>Purpose</u>. This method provides a means of judging the relative resistance of glass encapsulated electronic components to cracking under conditions of thermal stress. It employs immersion in a hot liquid then water to simulate the thermal stresses associated with both device manufacturing processes and end user assembly procedures.

2. <u>Apparatus</u>. Liquid baths shall be used which are capable of providing and maintaining the specified temperatures in the working zone when loaded with a maximum load. Bath temperatures under maximum load conditions shall be verified as needed to validate bath performance. Liquid composition shall be as specified herein.

3. <u>Procedure</u>. Remove any paint or other surface coatings. Clean test specimens using a general purpose cleaner/degreaser and rinse in water then acetone. Subsequent to cleaning, specimens shall be placed into the baths defined in table I for the applicable test condition using a dipping tool that will not significantly heat sink the body of the device under test. Specimens shall be fully immersed in the first bath for the specified period of time then transferred immediately to and fully immersed in the second bath. Unless otherwise specified, the test shall be considered complete upon removal of the specimen from the second bath.

3.1 <u>Timing</u>. Specimens shall be immersed into and removed from the first (hot) bath at a rate of  $1.0 \pm 0.5$  inch (25.4 ±12.7 mm) per second. The maximum dwell time above the hot bath prior to immersion shall be 7.0 seconds. Dwell time in the hot bath shall be 6 ±1.0 seconds. Specimens shall be released completely into the second bath within 3 seconds of their removal from the hot bath.

4. <u>Failure criteria</u>. Specimens that fail to meet the glass crack criteria of method 2074 of MIL-STD 750 shall be considered rejects.

- 5. <u>Summary</u>. The following shall be specified in the applicable performance specification.

- a. Sample size and acceptance number.

- b. Test condition.

- c. Special fixturing as applicable.

d. Number of test cycles if other than 1 cycle.

TABLE I. Conditions and temperatures.

| Step |                           | Test condition and temperatures |                              |

|------|---------------------------|---------------------------------|------------------------------|

|      |                           | А                               | В                            |

| 1    | Temperature and tolerance | 100°C ±5°C                      | 235°C ±5°C                   |

|      | Recommended fluid         | Water                           | Molten solder                |

| 2    | Temperature and tolerance | 0°C ±5°C                        | $25^{\circ}C \pm 5^{\circ}C$ |

|      | Recommended fluid         | Water                           | Water                        |

## METHOD 2071.6

# VISUAL AND MECHANICAL

1. <u>Purpose</u>. The purpose of this test is to verify the workmanship of hermetically packaged devices. This method shall also be utilized to inspect for damage due to handling, assembly, and test of the packaged device. This test is normally employed at outgoing inspection within the device manufacturer's facility, or as an incoming inspection of the assembled device.

2. <u>Apparatus</u>. Apparatus used in this test shall be capable of demonstrating device conformance to the applicable requirements of the individual specification. This includes optical equipment capable of magnification of 3X minimum to as specified herein, with a large field of view such as an illuminated ring magnifier.

3. <u>Procedure</u>. Unless otherwise specified, the device shall be examined under a magnification of 3X minimum. The field of view shall be sufficiently large to contain the entire device and allow inspection to the criteria listed in 3.1. Where inspection at a lower magnification reveals an anomaly, then inspection at a higher magnification (10X maximum, unless otherwise specified) may be performed to determine acceptability.

When a disposition is in doubt for any dimensional criteria, that dimension may be measured for verification.

3.1 Failure criteria. Devices which exhibit any of the following shall be considered rejects.

3.1.1 <u>Rejects</u>. Device construction (package outline), lead (terminal), identification, markings (content, placement, and legibility), and workmanship not in accordance with the applicable specification shall be rejected. This includes the following:

- a. Any misalignment of component parts to the extent that the package outline drawing dimensions are exceeded.

- b. Visual evidence of corrosion or contamination. Discoloration is not sufficient cause for rejection. The presence of lead carbonate formations in the form of a white/yellow crystalline shall be considered evidence of contamination.

- c. Damaged or bent leads or terminals which precludes their use in the intended application.

- d. Defective finish: Evidence of blistering, or evidence of nonadhesion, peeling, or flaking which exposes underplate or base metal.

- e. Burrs that will cause lead or terminal dimensions to be exceeded.

- f. Foreign material (including solder or other metallization) bridging leads or otherwise interfering with the normal application of the device. Where adherence of foreign material is in question, devices may be subjected to a clean filtered air stream (suction or expulsion) or an isopropyl alcohol wash and then reinspected.

- g. Protrusions beyond seating plane that will interfere with proper seating of the device.

- h. Missing welds or crimps.

- i. Damage causing distortion of a flange beyond its normal configuration.

- j. Damage to a stud (thread damage or bending) which restricts normal mounting.

- k. Dents in metal lids which precludes their use in the intended application or causing a defect in the finish (see 3.1.1.d).

- I. Gaps, separations, or other openings that are not part of the normal design configuration.

- m. Tubulation weld: Any fracture or split in the tubulation weld.

- n. Weld alignment: Base weld mating surfaces not parallel, or that precludes intended use.

- 3.1.1.1 Failure criteria for lead/terminal seal area of metal can devices.

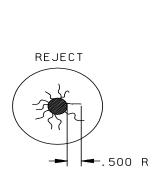

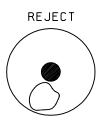

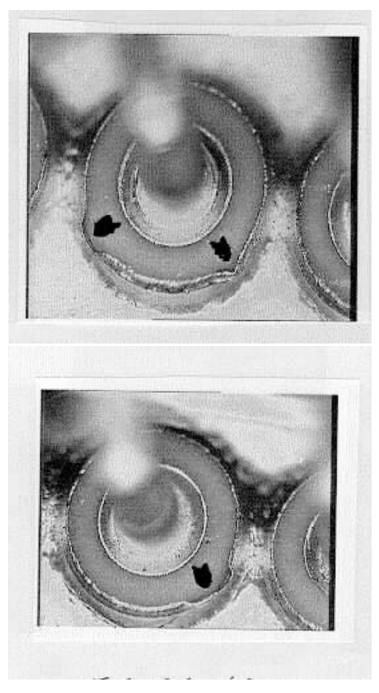

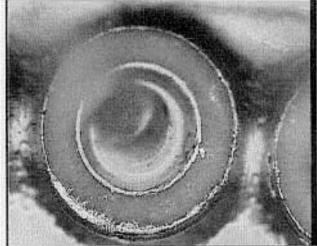

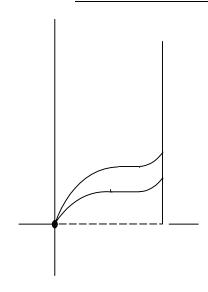

- a. Radial cracks (except meniscus cracks) that extend more than one-half of the distance from the pin to the outer member (see figure 2071-1). Radial cracks that originate from the outer member.

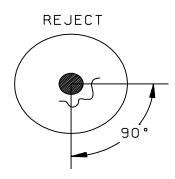

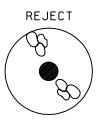

- b. Circumferential cracks (except meniscus cracks) that extend more than 90 degrees around the seal center (see figure 2071-2).

- c. Open surface bubble(s) in strings or clusters that exceed two-thirds of the distance between the lead and the package wall.

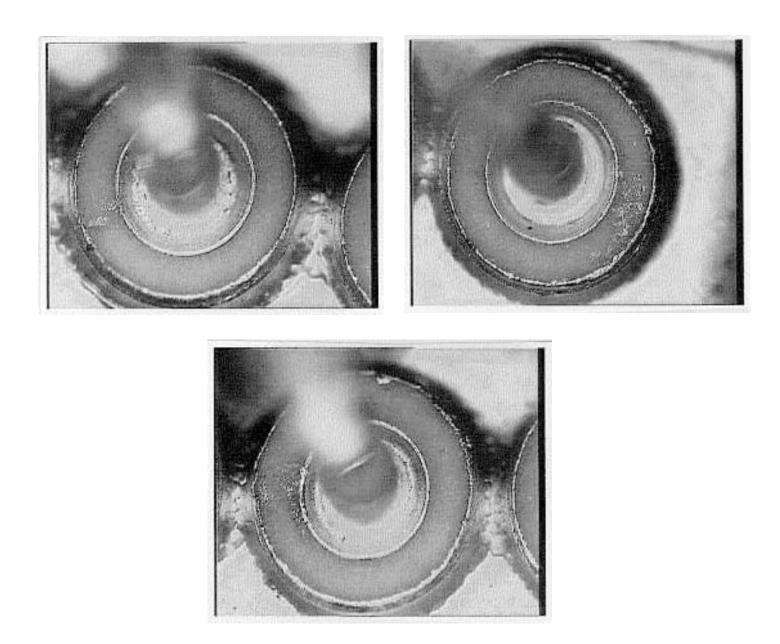

- d. Visible subsurface bubbles that exceed the following:

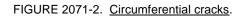

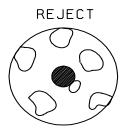

- (1) Large bubbles or voids that exceed one-third of the glass sealing area (see figure 2071-3).

- (2) Single bubble or void that is larger than two-thirds of the distance between the lead and the package wall at the site of the inclusion and extends more than one-third of the glass seal depth (see figure 2071-4).

- (3) Two bubbles in a line totaling more than two-thirds of the distance from pin to case (see figure 2071-5).

- (4) Interconnecting bubbles greater than two-thirds of the distance between pin and case (see figure 2071-6).

- e. Except as designed, reentrant seals which exhibit non-uniform wicking or negative wicking.

- f. Twenty-five percent or greater of the radius length from the center of the feedthrough to the edge of the glass eyelet.

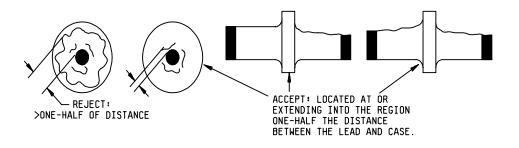

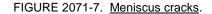

- g. Glass meniscus cracks that are not located within one-half of the distance between the lead to the case (see figure 2071-7). The glass meniscus is defined as that area of glass that wicks up the lead or terminal.

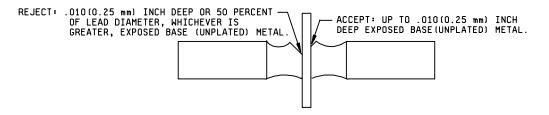

- h. Any chip-out of ceramic or sealing glass that penetrates the sealing glass deeper than the glass meniscus plane. Exposed base metal as a result of meniscus chip outs are acceptable if the exposed area is no deeper than 0.010 inch (0.25 mm) or 50 percent of lead diameter, whichever is greater (see figure 2071-8).

3.1.1.2 <u>Failure criteria for ceramic packages</u>. Failure criteria for ceramic packages (see method 2009 of MIL-STD-883).

3.1.1.3 <u>Failure criteria for opaque glass body devices</u>. Failure criteria for opaque glass body devices (see method 2068 of MIL-STD-750).

METHOD 2071.6 12 November 2002

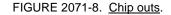

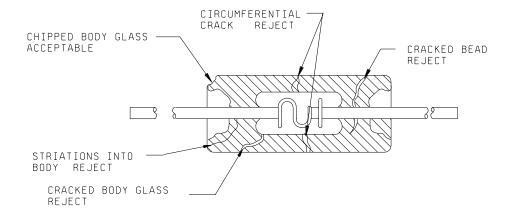

- \* 3.1.1.4 Transparent glass diodes, double plug construction.

- a. Any evidence of a crack, fracture, or a chipout closer to the die than 50 percent of the designed seal length shall be rejected. Area of examination shall be as shown on figure 2071-9.

- b. Any crack that terminates in the axial direction is cause for rejection

- c. Meniscus cracks are not cause for rejection.

- d. Any chip out that exposes base metal shall be rejected.

\* 3.1.1.5 <u>Transparent glass diodes, large cavity (i.e. S-bend, C-bend, or straight-through constructions).</u> Any crack or fracture in the glass over the area of the device cavity shall be rejected.

- a. Any crack or fracture in the glass over the area of the device cavity shall be rejected.

- b. Any chip out that exposes base metal shall be rejected (this does not apply to chipouts at either end of device where glass joins external lead).

- c. Any crack that terminates in the axial direction is cause for rejection.

- d. Meniscus cracks are not cause for rejection.

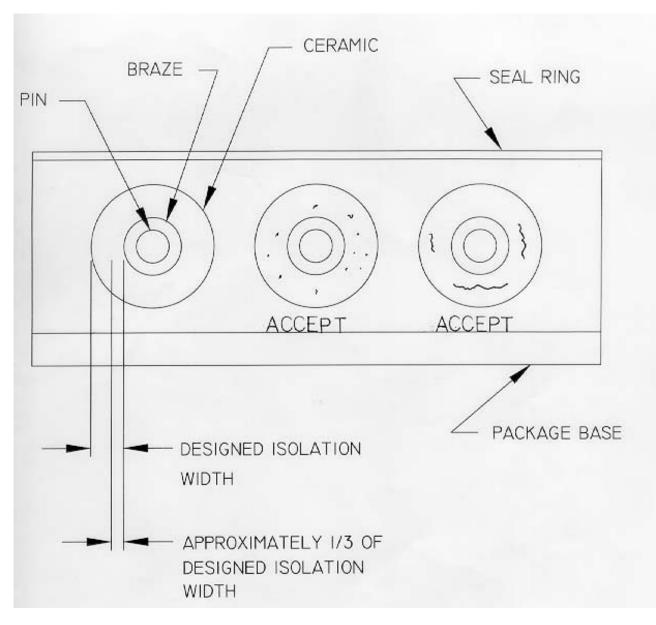

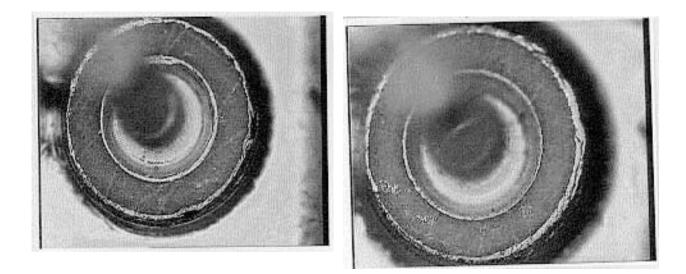

- 3.1.1.6 Failure criteria for hermetic packages with ceramic eyelet feedthroughs.

- a. Any separation or delamination of the braze metallization from the inner diameter (ID) or outer diameter (OD) of the ceramic eyelet (see figures 2071-10 and 2071-11).

- b. Any cracks or separation in the braze between the ceramic eyelet ID and the lead or the ceramic eyelet OD and the package. Any voids, depressions, or pinholes the bottom of which cannot be seen at 30X maximum magnification in the braze between the ceramic eyelet ID and the lead or the ceramic eyelet OD and the package.

- c. Any discontinuation in the braze from the ceramic eyelet ID to the lead or the ceramic eyelet OD to the package exposing unplated metallization or bare ceramic.

- d. Any conductive material attached to the ceramic eyelet that reduces the designed isolation width by more than one-third unless it is demonstrated that the device voltage isolation requirement can be met with less than two-thirds of the width of the ceramic eyelet (see figures 2071-16 through -26).

- e. Any metallization that extends beyond the height of the ceramic that is not adhered to the ceramic.

- f. No cracks are allowed. Chipouts greater than .005 inches (0.127 mm) in any direction are not allowed.

- 4. <u>Summary</u>. The following details shall be specified in the applicable acquisition document:

- a. Requirements for markings and the lead (terminal) or pin identification.

- b. Detailed requirements for materials, design, construction, and workmanship.

- c. Magnification requirements, if other than specified.

FIGURE 2071-1. Radial cracks extending more than one-half the distance from pin to outer member.

FIGURE 2071-3. Bubbles in glass exceeding one-third of the sealing area.

FIGURE 2071-4. Single bubble or void.

FIGURE 2071-5. Two bubbles in a line.

FIGURE 2071-6. Interconnecting bubbles.

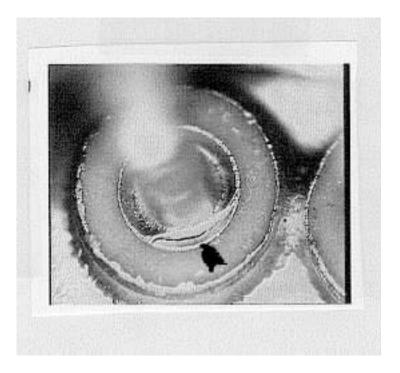

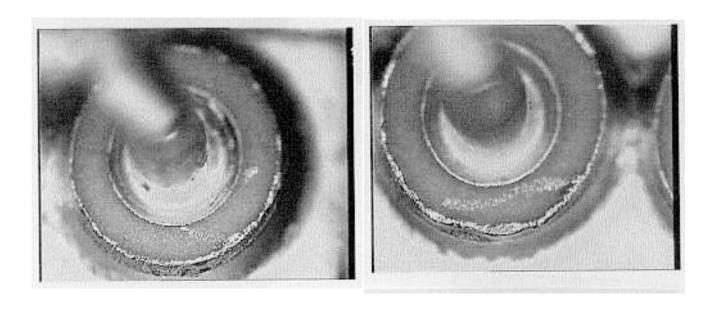

Arrows on both pictures illustrate rejectable conditions of braze separation/delamination.

FIGURE 2071-10. Braze separation/delamination.

Reject: Arrow indicates a crack on the inner diameter braze metallization of the ceramic eyelet.

FIGURE 2071-11. Crack (braze metallization.

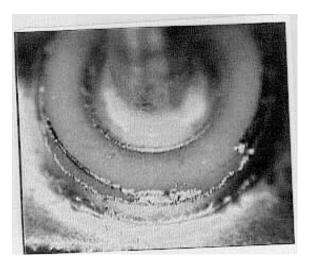

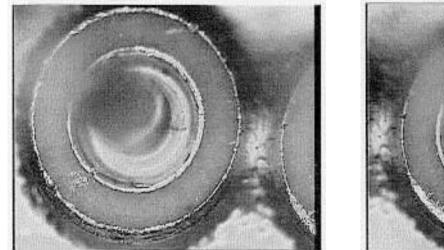

Reject: All three figures illustrate discontinuous braze metallization on the outer diameter of the ceramic eyelet.

FIGURE 2071-12. Discontinuous braze metallization.

METHOD 2071.6 12 November 2002

FIGURE 2071-13. Ceramic feedthrough visual inspection criteria.

Reject: All figures indicate rejectable foreign material conditions.

FIGURE 2071-14. Rejectable foreign material conditions.

METHOD 2071.6 12 November 2002

Reject: All figures indicate rejectable foreign material conditions.

FIGURE 2071-14. Rejectable foreign material conditions .

METHOD 2071.6 12 November 2002

Reject: All figures indicate rejectable foreign material conditions.

FIGURE 2071-14. Rejectable foreign material conditions.

### METHOD 2074.4

#### INTERNAL VISUAL INSPECTION (DISCRETE SEMICONDUCTOR DIODES)

1. <u>Purpose</u>. The purpose of this test is to check the materials, design, construction, and workmanship of discrete semiconductor diodes and other two-terminal semiconductor devices described herein. All tests shall be performed to detect and eliminate those devices with defects that could lead to device failures. Opaque glass type constructions shall be examined before encapsulation. (After encapsulation, see method 2068 of MIL-STD-750). Metal can devices shall be examined before capping. (After capping or sealing, see method 2071 of MIL-STD-750). Clear glass construction shall be examined after encapsulation.

- 2. Apparatus.

- a. The apparatus for these tests shall include optical equipment and any visual standards (e.g., gauges, drawings, photographs) necessary to perform an effective examination and enable the operator to make objective decisions on the acceptability of the device being examined. Any necessary fixturing for handling devices during examination to promote efficient operation without damaging the units shall be provided.

- b. A monocular, binocular, or stereo microscope capable of magnification from 20X minimum to 30X maximum, shall be used unless otherwise specified. The inspection shall be performed under suitable illumination.

\* 3. <u>Procedure</u>. The devices shall be examined at the specified magnifications to determine compliance with the requirements of the applicable sections of this test method based on device construction. Examinations for transparent body devices may be performed anytime prior to body coating or painting. Axial construction devices shall be viewed at approximate right angles to their major axis while being rotated through 360 degrees. For the time interval, if any, between visual inspection and package sealing, devices shall be stored, handled, and processed in a manner to avoid contamination and to preserve the integrity of the devices as inspected.

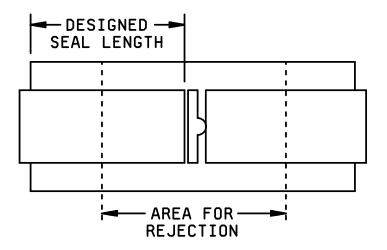

- \* 3.1 Die criteria (applicable to all body styles).

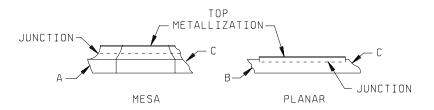

- a. Chipouts. Reject for chipouts that extend more than 50 percent of the way up the moat area (mesa devices) or that extend to within 2 mils of the junction. NOTE: Actual junction location will vary depending on specific device characteristics. (Figure 2074-1.)

ACCEPT: CHIPOUTS  $\leq$  50% UP MOAT AND  $\geq$  2 MILS FROM JUNCTION - "A" ACCEPT: CHIPOUTS  $\geq$  2 MILS FROM JUNCTION - "B" REJECT: CHIPOUTS  $\leq$  2 MILS FROM JUNCTION - "C"

\* FIGURE 2074-1. Chipouts.

METHOD 2074.4 12 November 2002

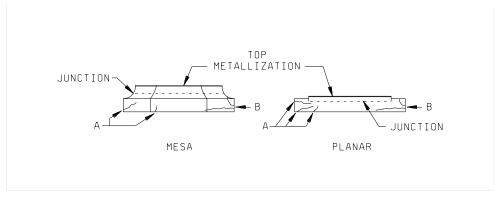

\* b. Cracks. Reject for cracks that extend to within 2 mils of the junction or propagate in the direction of the junction. NOTE: The junction may be in a different place than shown depending on specific device characteristics.

REJECT: CRACKS  $\leq$  2 MILS FROM JUNCTION OR PROPAGATING TOWARD JUNCTION -"A" ACCEPT: CRACKS  $\geq$  2 MILS FROM JUNCTION AND PROPAGATING AWAY FROM JUNCTION -"B"

## \* FIGURE 2074-2. Cracks.

- \* 3.2 <u>Applicable body styles</u>. The devices shall be examined in accordance with the following addendums as applicable for the body style involved.

- Addendum A Axial lead, transparent body, pressure contact design

- Addendum B Axial lead, transparent body straight through lead to die contact

- Addendum C Axial lead and surface mount, double plug transparent body (dumet plug, round end cap, soft glass)

- Addendum D Axial lead and surface mount, double plug transparent body (tungsten or molybdenum plug, square end cap, hard glass)

- Addendum E Axial lead, transparent body, point contact

- Addendum F Axial lead, double plug, opaque body, power rectifier and regulator

- Addendum G Metal body, axial lead, solder contact design

- Addendum H Metal body, stud mounted, solder contact design

- Addendum I Metal body, diamond base regulators, solder contact design

- 4. Summary.

- a. Detailed requirements for materials, design, construction, and workmanship.

- b. Magnification requirements, if other than specified.

# APPENDIX A

#### SMALL SIGNAL, COMPUTER, REGULATOR, LOW POWER RECTIFIERS, AND MICROWAVE DIODES

A.1 <u>Axial lead, transparent body, pressure contact design.</u> The following examinations shall be made after encapsulation (C and S bend whisker).

A.1.1 <u>Glass cracks and chips (see figure 2074-A1)</u>. No cracks shall be allowed in the vicinity of the cavity. Any crack originating at either end of the package or crack that extends into the body of the glass toward the cavity more than 25 percent of the glass-to-glass or glass-to-metal seal length shall be cause for rejection. Any glass chip deep enough to expose the plug or lead surface and extending longitudinally into the glass-to-metal seal toward the cavity to reduce the effective seal length to less than one external lead diameter shall be cause for rejection.

A.1.2 <u>Incomplete seal</u>. All devices shall be inspected for glass-to-metal seal or glass-to-glass seal. Both seals shall be a minimum of one external lead diameter over the entire sealed portion (sealed interface).

A.1.3 <u>Bubbles in seal</u>. All devices shall be inspected for bubbles in the glass-to-metal or glass-to-glass seal. A series of bubbles that reduce the effective seal length to less than one external lead diameter shall be cause for rejection. Bubbles in the glass, but not effecting the glass-to-glass or glass-to-metal seal area, are not cause for rejection.

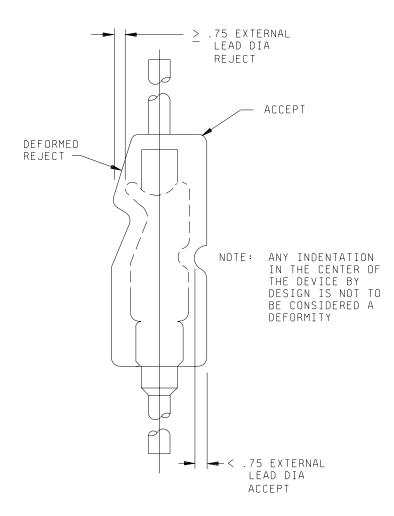

A.1.4 <u>Glass package deformities (see figure 2074-A2)</u>. Any glass envelope deformity equal to or greater than 75 percent of the external lead diameter shall be cause for rejection.

A.1.5 <u>Extraneous matter</u>. A device shall be rejected if there are unattached solder balls, semiconductor material, chips, flaked plating, or opaque material that is larger than the smallest distance between exposed active areas.

\*FIGURE 2074-A1. Glass cracks and chips.

# APPENDIX A

\* FIGURE 2074-A2. Package deformities.

# APPENDIX A

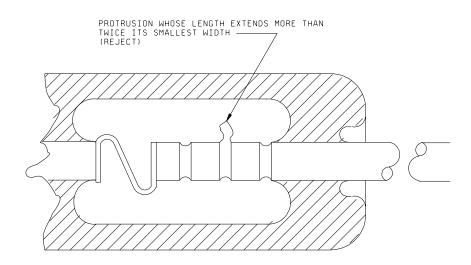

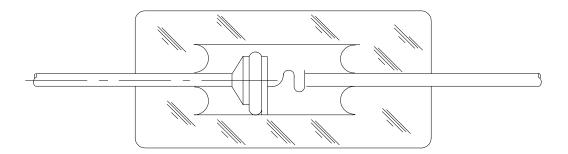

A.1.6 <u>Solder protrusions (see figure 2074-A3)</u>. All devices shall be inspected for solder protrusions. Any device with a protrusion that extends more than twice the smallest protrusion width shall be rejected.

\* FIGURE 2074-A3. Solder protrusions.

A.1.7 <u>Pressure contact defects</u>. The following misalignments or deformations shall be cause for rejection:

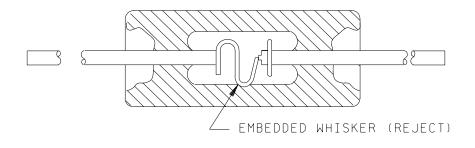

a. Whisker embedded within glass body wall (see figure 2074-A4).

\* FIGURE 2074-A4. Embedded whisker.

# APPENDIX A

b. Toe contact between base of S or C spring and top surface of die caused by insufficient loading (see figure 2074-A5).

\* FIGURE 2074-A5. Toe contact.

c. Toe contact on top surface of die (see figure 2074-A6).

\* FIGURE 2074-A6. Toe contact on top surface of die.

METHOD 2074.4 12 November 2002

# APPENDIX A

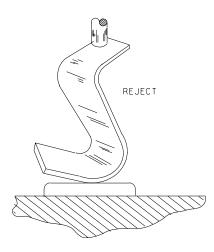

d. Heel contact between base of S or C spring and top surface of die (see figure 2074-A7).

- \* FIGURE 2074-A7. Heel contact.

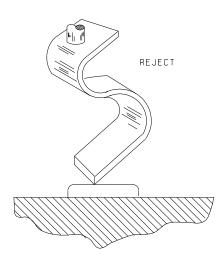

- e. Point contact between base of S or C spring and top surface of die except by design (deformed or twisted whisker) (see figure 2074-A8).

\* FIGURE 2074-A8. Point contact.

# APPENDIX A

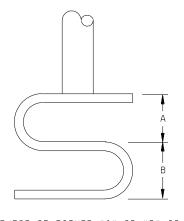

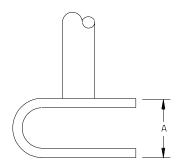

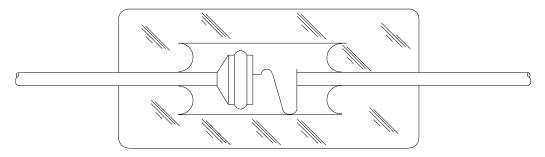

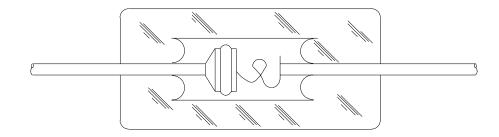

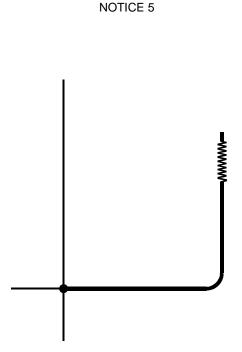

f. Design compressed height (see figures 2074-A9 and 2074-A10). Either half of an S or C bend that is compressed so that any dimension is reduced to less that 50 percent of its design shall be rejected.

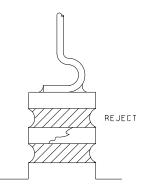

REJECT IF EITHER "A" OR "B" IS LESS THAN 50% OF ITS DESIGN COMPRESSED HEIGHT

\* FIGURE 2074-A9. "S" whisker compressed height.

REJECT IF EITHER "A" IS LESS THAN 50% OF ITS DESIGN COMPRESSED HEIGHT

\* FIGURE 2074-A10. "C" bend compressed height.

### APPENDIX A

A.1.8 <u>Whisker weld to post</u>. Any device that exhibits weld splash or splatter (teardrop or balled) between whisker and post shall be rejected when it exceeds 25 percent of nominal lead diameter. The profile of the whisker weld to post shall not allow light penetration by more than 50 percent of lead diameter when using back lighting techniques.

A.1.9 <u>Die to post or die to die contact area</u>. Solder shall not be rough in appearance and shall be fused to a minimum of one-half the available bonding perimeter. Any solder overflow that touches the opposite surface of the die or dice shall be cause for rejection.

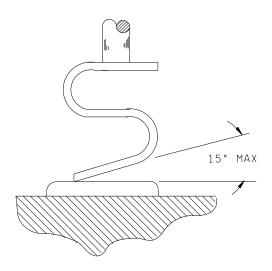

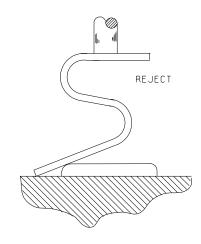

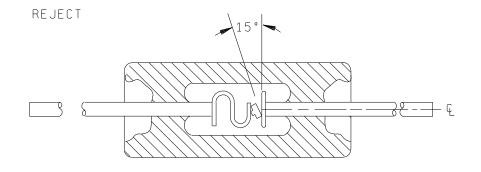

A.1.10 <u>Die alignment (see figure 2074-A11)</u>. A device shall be rejected if the die surface is not within 15° of being normal to the centerline of the mounting post.

## \* FIGURE 2074-A11. Die alignment.

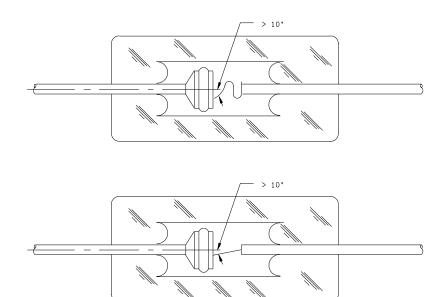

A.1.11 Lead alignment defects, (applicable to that portion of each lead within the glass envelope). A device lead which is either misaligned or bent so that it makes an angle with the principle device axis greater than 10 degrees shall be rejected.

A.1.12 <u>Multiple chip attachment defects</u>. A multiple chip stack that tilts more than 10 degrees from the principle axis of the device shall be cause for rejection.

### APPENDIX B

# SMALL SIGNAL, COMPUTER, REGULATOR, LOW POWER RECTIFIERS, AND MICROWAVE DIODES.

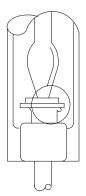

B.1 <u>Axial lead transparent body straight through lead to die contact (see figure 2074-B1)</u>. The following criteria shall be specified for the straight through construction after encapsulation but before body coating or painting.

B.1.1 <u>Glass cracks and chips (see figure 2074-A1)</u>. No cracks shall be allowed in the vicinity of the cavity. Any crack originating at either end of the package or crack that extends into the body of the glass toward the cavity more than 25 percent of the glass-to-glass or glass-to-metal seal length shall be cause for rejection. Any glass chip deep enough to expose the plug or lead surface and extending longitudinally into the glass-to-metal seal toward the cavity to reduce the effective seal length to less than one external lead diameter shall be cause for rejection.

B.1.2 <u>Incomplete seal</u>. All devices shall be inspected for glass-to-metal seal or glass-to-glass seal. Both seals shall be a minimum of one external lead diameter over the entire sealed portion (sealed interface).

B.1.3 <u>Bubbles in seal</u>. All devices shall be inspected for bubbles in the glass-to-metal or glass-to-glass seal. A series of bubbles that reduce the effective seal length to less than one external lead diameter shall be cause for rejection. Bubbles in the glass, but not effecting the glass-to-glass or glass-to-metal seal area, are not cause for rejection.

B.1.4 <u>Glass package deformities (see figure 2074-A2)</u>. Any glass envelope deformity equal to or greater than 75 percent of the external lead diameter shall be cause for rejection.

B.1.5 <u>Extraneous matter</u>. A device shall be rejected if there are unattached solder balls, semiconductor material, chips, flaked plating, or opaque material that is larger than the smallest distance between exposed active areas.

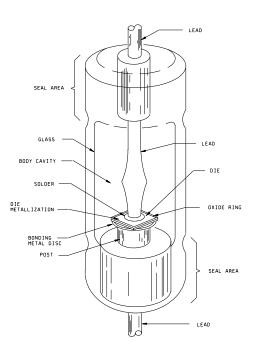

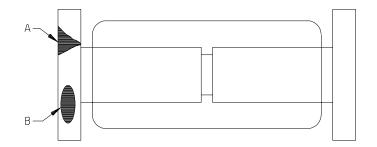

\* FIGURE 2074-B1. Internal construction.

# APPENDIX B

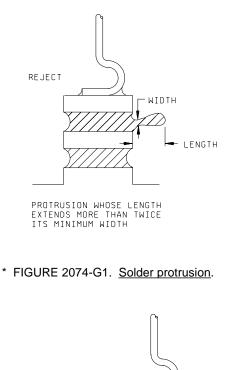

# B.1.6 Die to post solder connection.

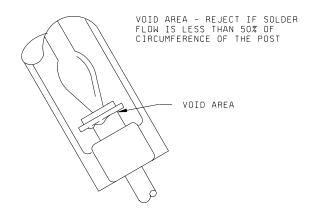

a. Solder voids (see figure 2074-B2). A device shall be rejected if solder flow is less than 50 percent of the perimeter of the minimum available contact area of the post.

- \* FIGURE 2074-B2. Solder voids.

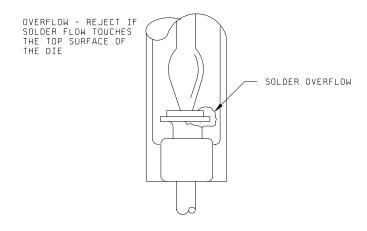

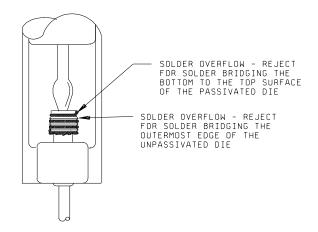

- b. Solder overflow (see figure 2074-B3). A device shall be rejected if any solder flow touches the opposite surface of the die.

\* FIGURE 2074-B3. Solder bridge.

# APPENDIX B

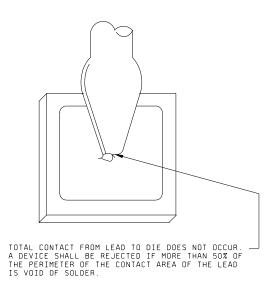

B.1.7 Lead to die solder connection (see figure 2074-B4). A device shall be rejected if more than 50 percent of the perimeter of the available contact area of the lead is void of solder.

- \* FIGURE 2074-B4. Solder voids.

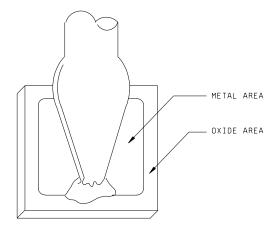

- a. Solder overflow (see figure 2074-B5). A device shall be rejected if solder flow extends beyond 50 percent of the distance from the metal to the outer edge of the oxide.

\* FIGURE 2074-B5. Solder overflow.

### APPENDIX B

b. Solder protrusion, slivers, and spikes (see figure 2074-B6). A device shall be rejected if solder slivers and spikes are not securely attached to the main body. A securely attached sliver of spike is one having a cross sectional area greater at the area of attachment than anywhere else on the solder protrusion and having no necked down areas. Solder protrusions, slivers, and spikes whose length exceeds twice the smallest width of attachment shall be rejected.

\* FIGURE 2074-B6. Solder slivers and spikes.

c. Solder balls. A device shall be rejected if there are any insecurely attached solder balls. An insecurely attached solder ball is one whose major cross sectional area is more than twice the cross sectional area of the attachment.

B.1.8 Die to die solder connection (see figure 2074-B7). A device shall be rejected if more than 50 percent of the perimeter of the available contact area of the die is void of solder.

\* FIGURE 2074-B7. Die to die solder connection.

### APPENDIX C

### \* SMALL SIGNAL, COMPUTER, REGULATOR, LOW POWER RECTIFIERS, AND MICROWAVE DIODES

# \* C.1 Axial lead and surface mount, double plug, transparent body (, dumet plug, round end cap, soft glass).

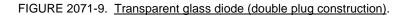

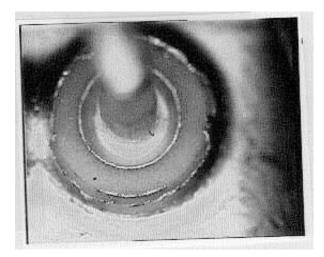

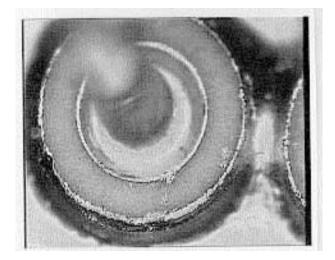

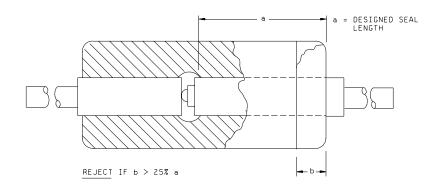

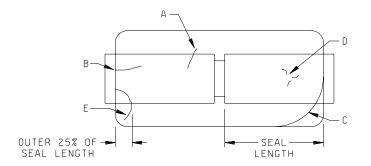

C.1.1 <u>Glass cracks (see figure 2074-C1)</u>. No cracks shall be allowed within 0.010 inch of the die. Any spiral or meniscus crack originating at either end of the package or glass that extends into the body of the glass toward the die more than 25 percent of the designed seal length shall be cause for rejection. Any chip deep enough to expose the plug surface and extending longitudinally into the glass toward the die more than 25 percent of the designed seal length shall be cause for rejection.

\* FIGURE 2074-C1. Glass cracks.

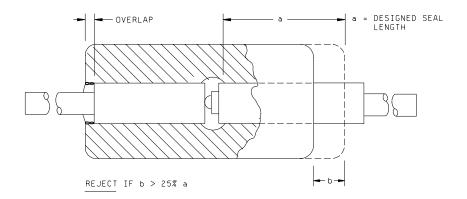

C.1.2 <u>High seal (see figure 2074-C2)</u>. Any device which displays a glass case off center condition reducing the seal band of either plug by more than 25 percent of its designed length shall be cause for rejection.

\* FIGURE 2074-C2. High seal.

METHOD 2074.4 12 November 2002

14

# APPENDIX C

C.1.3 <u>Insufficient seal (see figure 2074-C3)</u>. Any anomaly such as bubbles, plug blisters, separations, leaching, or undersealing that affects the combined seal length of either plug by reducing the a sealing band to less than 50 percent of the designed seal length on any package type shall be cause for rejection.

\* FIGURE 2074-C3. Insufficient seal.

# APPENDIX C

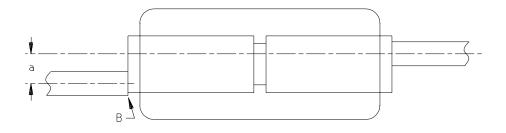

C.1.4 <u>Plug alignment (see figures 2074-C4 and 2074-C5)</u>. All devices shall be inspected for proper plug alignment. A plug displacement distance more than 25 percent of the diameter of the plug shall be cause for rejection. The plug shall not tilt to the degree that it touches the chip or is misaligned from the other plug axis more than 5 degrees.

\* FIGURE 2074-C4. Plug alignment.

\* FIGURE 2074-C5. Plug displacement.

C.1.5 <u>Extraneous matter</u>. A device shall be rejected if there are unattached solder balls, semiconductor material, chips, flaked plating, or opaque material that is larger than the smallest distance between exposed active areas.

### APPENDIX C

C.1.6 <u>Lead connections (see figure 2074-C6)</u>. Lead to plug connections shall be inspected for incomplete welds. Any partial welds less than 75 percent of total weld area shall be cause for rejection.

\* FIGURE 2074-C6. Incomplete weld.

### C.1.7 Die defects (reject).

C.1.7.1 Die tilt greater than 5 degrees or slug or preform makes contact to chip on bump side.

C.1.7.2 Any die that exhibits chip outs exceeding .25 inch (6.35 mm) the die width or extending to within 2 mils of the junction shall be rejected.

\* C.1.8 Criteria for round end cap surface mount devices.

C.1.8.1 Glass to metal seal shall be .015 inch (0.381 mm) min for DO-213AA and .020 inch (0.508 mm) min for DO-213AB, around the diameter of each slug.

C.1.8.2 Slug exposure shall not exceed 30 percent of the slug length (.014 inch (0.3556 mm) min for DO-213AA and .022 inch (0.5588 mm) min for DO-213AB).

C.1.8.3 There shall be no cracks in the device within .010 inch (0.254 mm) of the die.

C.1.8.4 There shall be no cracks in the glass that are pointed towards the die.

C.1.8.5 There shall be no conductive contaminants in the die cavity area.

C.1.8.6 For plug alignment, including end caps, see C.1.4.

C.1.8.7 For end cap connections, see C.1.6.

# APPENDIX D

# \* (ALL, COMPUTER, REGULATOR, RECTIFIER, AND MICROWAVE DIODES)

\* D.1.0 <u>Axial lead and surface mount double plug, transparent body (tungsten or molybdenum plug, square end cap, hard glass).</u>

- \* D.1.1 Glass.

- \* a. Cracks. Spiral or longitudinal cracks of any length originating at either end that propagate in the direction of the die are cause for rejection. Reject for cracks that are not confined to the glass surface or the outer 25 percent of the seal length. Cracks confined to the outer 25 percent of the designed seal length that propagate back toward the starting edge (away from the die area) are acceptable. Small surface impact marks, "c" cracks and microcracks are acceptable if they are confined to the glass surface with no other cracks radiating from them are acceptable. (Figure 2075-D1.)

REJECT: CRACKS NOT CONFINED TO SURFACE OR OUTER 25% OF SEAL LENGTH - "A" REJECT: CRACKS OF ANY LENGTH THAT PROPAGATE TOWARD DIE - "B" REJECT: SPIRAL CRACKS PROPAGATING TOWARD DIE - "C" ACCEPT: SMALL C-CRACKS OR MICRO CRACKS IN GLASS SURFACE - "D" ACCEPT: CRACKS IN OUTER 25% OF SEAL LENGTH THAT PROPAGATE AWAY FROM DIE - "E"

\* FIGURE 2074-D1. Cracks.

### APPENDIX D

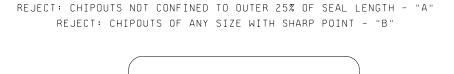

\* b. Chipouts. Edge chipouts that expose a plug and are not confined to the outer 25 percent of the designed seal length are cause for rejection. Edge chipouts (regardless of size) that expose a plug and create a sharp angle or "V" shape that points toward the die area are rejects (Figure 2074-D2).

- \* FIGURE 2074-D2. Chipouts.

- \* c. Holes. Any hole over the die or slug area greater that 50 percent of the glass thickness in depth is cause for rejection except that holes of any depth are acceptable in the outer 25 percent of the designed seal length.

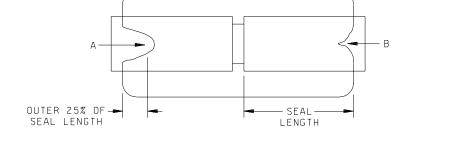

- \* d. Deformities. Any glass surface deformity that causes the glass surface to be displaced by more than 10 percent of the designed glass diameter or that results in the device not meeting a dimensional requirement is cause for rejection. (Figure 2074-D3.)

<sup>\*</sup> FIGURE 2074-D3. Deformity.

### APPENDIX D

\* e. Surface damage and discoloration. Any device with surface abrasions, chips, scratches, rough or discolored (darkened) glass over the die area that result in the die not being clearly visible is a reject. Using liquid immersion to improve die visibility is acceptable.

### D.1.2 Seal.

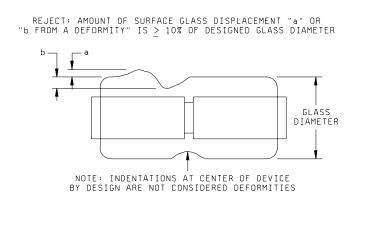

\* a. Glass positioning and missing glass. Off center glass and/or portions of missing glass that reduce the seal length on either plug by more than 25 percent of the designed seal length is cause for rejection. (Figure 2074-D4.)

REJECT: GLASS OFF CENTER AND/OR MISSING GLASS THAT REDUCES SEAL LENGTH BY  $\geq$  25% - "A"

\* FIGURE 2074-D4. Positioning.

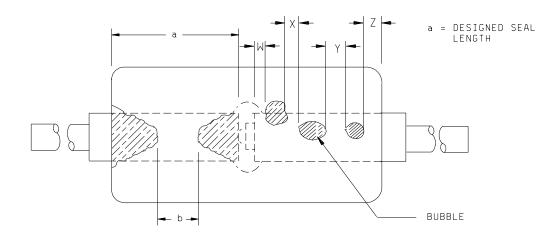

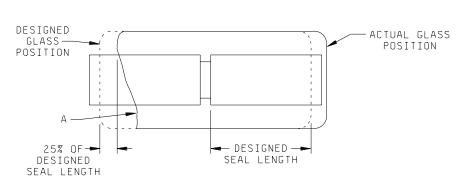

\* b. Insufficient seal. Seal surface anomalies such as undercut, separations, plug blisters, scratches or cracks, bubbles, silicon chips, fibers, or missing plating which, when combined, reduce the sealing length along any linear path to less than 50 percent of the designed seal length are cause for rejection. NOTE: Lines or "strings" of small bubbles are considered to be seal anomalies for the entire length of the line. (Figure 2074-D5.)

# APPENDIX D

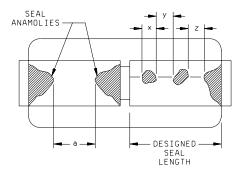

# REJECT: SEAL LENGTH "a" REDUCED TO $\leq$ 50% OF DESIGNED SEAL LENGTH REJECT: COMBINED SEAL LENGTHS "x"+"y"+"z" ALONG ANY LINE < 50% OF DESIGNED SEAL LENGTH

- \* FIGURE 2074-D5. Insufficient seal.

- \* c. Extraneous or loosely attached materials. Any unattached or loosely attached solder, braze, silicon chips, flaked plating, fibers or other opaque extraneous material in the die cavity (for cavity devices) that is greater than 1 mil in any dimension are cause for rejection. No solder, braze or other bonding materials shall extend from a plug into the area between plugs.

D.1.3 <u>Alignment</u>. NOTE: Any die to plug non-contact that occurs as a result of die or plug misalignment is most accurately evaluated by thermal impedance testing. In cases where pass/fail status of a device is unclear based on the alignments requirements presented herein, thermal impedance testing may be used to determine the acceptability of the device.

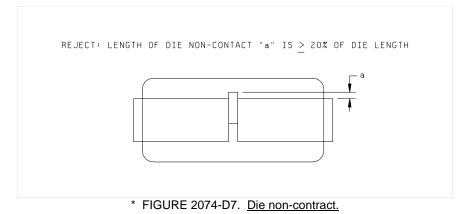

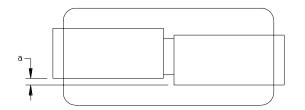

\* a. Die alignment: Any die that tilts more than 5 degrees with respect to the surface of either plug or that tilts sufficiently to make any unintended contact with the plug is cause for rejection. (Figure 2074-D6.) Any die that is out of axial alignment such that it extends beyond the slug more than 20 percent of its length or width is cause for rejection. (Figure 2074-D7)

\* FIGURE 2074-D6. Tilt.

# APPENDIX D

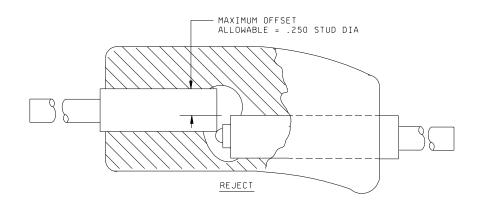

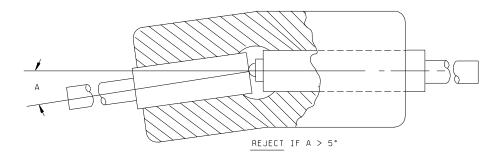

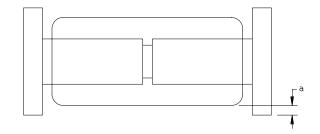

\* b. Plug alignment. Plugs that are not axially aligned other in the die area to within 1/8 (12.5 percent) of the diameter of the plug are cause for rejection. (Figure 2074-D8.) Any plug that tilts more than 5 degrees with respect to the other or that tilts sufficiently to make any unintended contact with the die is cause for rejection (Figure 2074-D9).

REJECT: PLUG OFFSET "a" IS > 1/8(12.5%) OF PLUG DIAMETER

\* FIGURE 2074-D8. Plug offset.

# APPENDIX D

REJECT: PLUG TILT ANGLE "a" IS > 5°

### \* FIGURE 2074-D9. Plug tilt angle.

# D.1.4 Lead and end cap attach.

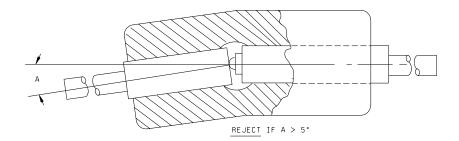

\* a. Lead alignment (leaded devices). Leads that are not axially aligned to within one lead diameter or leads that are not contained completely within the diameter of the plug are cause for rejection (Figure 2074-D10).

REJECT: LEAD OFFSET "a" IS GREATER THAN ONE LEAD DIAMETER REJECT: LEAD IS NOT COMPLETELY CONTAINED WITHIN PLUG DIAMETER "B"

\* FIGURE 2074-D10. Lead offset.

# APPENDIX D

- \* b. Braze (leaded devices). Leads that are not brazed to the plug around at least 90 percent of the lead perimeter are cause for rejection. Any cracks or fissures in the braze are cause for rejection. Pin holes in the braze are acceptable.

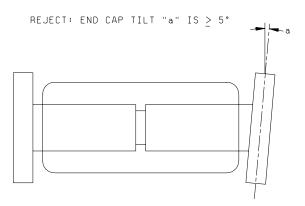

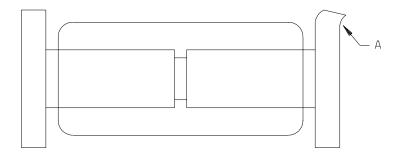

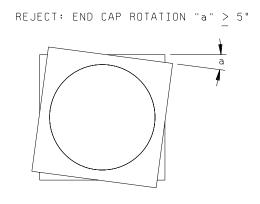

- \* c. End caps (surface mount). Reject for end caps that do not allow at least 3 mils clearance from the glass body to the mounting surface on all four sides (Figure 2074-D11). Reject for end caps that are not perpendicular to the plugs to within 5 degrees (Figure 2074-D12). Reject for end caps that are bent sufficiently to cause the device to exceed any specified diode or end cap dimension (Figure 2074-D13). Reject for end cap rotation where mounting surfaces are not co-planer to each other to within 5 degrees (Figure 2074-D14). Reject for tabs that have indentations, holes or other damage effecting more than 25 percent of any mounting surface (Figure 2074-D15). Reject for end caps that exhibit flaking, blistering or peeling.

\* FIGURE 2074-D11. End cap clearance.

\* FIGURE 2074-D12. End cap tilt.

# APPENDIX D

REJECT: DEVICE WITH END CAP DEFORMATION THAT EXCEEDS ANY SPEIFIED DEMENSION - "A"

\* FIGURE 2074-D13. End cap deformation.

\* FIGURE 2074-D14. End cap rotation.

# APPENDIX D

REJECT: ANY MOUNTING SURFACE REDUCED TO  $\leq$  75% of It's designed area due to Nicks("A"), Pits("B"),ect.

\* FIGURE 2074-D15. Nicks.

### APPENDIX E

#### SMALL SIGNAL, COMPUTER, REGULATOR, LOW POWER RECTIFIERS, AND MICROWAVE DIODES

E.1 <u>Axial lead, transparent body, point contact</u>. The following additional criteria shall be specified for the point contact construction after encapsulation but before body coating or painting.

E.1.1 <u>Glass cracks and chips (see figure 2074-A1)</u> No cracks shall be allowed in the vicinity of the cavity. Any crack originating at either end of the package or crack that extends into the body of the glass toward the cavity more than 25 percent of the glass-to-glass or glass-to-metal seal length shall be cause for rejection. Any glass chip deep enough to expose the plug or lead surface and extending longitudinally into the glass-to-metal seal toward the cavity to reduce the effective seal length to less than one external lead diameter shall be cause for rejection.

E.1.2 <u>Incomplete seal</u>. All devices shall be inspected for glass-to-metal seal or glass-to-glass seal. Both seals shall be a minimum of one external lead diameter over the entire sealed portion (sealed interface).

E.1.3 <u>Bubbles in seal</u>. All devices shall be inspected for bubbles in the glass-to-metal or glass-to-glass seal. A series of bubbles that reduce the effective seal length to less than one external lead diameter shall be cause for rejection. Bubbles in the glass, but not effecting the glass-to-glass or glass-to-metal seal area, are not cause for rejection.

\* E.1.4 <u>Glass package deformities (see figure 2074-A2)</u>. Any glass envelope deformity equal to or greater than 75 percent of the external lead diameter shall be cause for rejection.

E.1.5 <u>Extraneous matter</u>. A device shall be rejected if there are unattached solder balls, semiconductor material, chips, flaked plating, or opaque material that is larger than the smallest distance between exposed active areas.

E.1.6 <u>Pressure contact defects</u>. The following misalignments or deformities shall be cause for rejection:

a. Whisker touches glass body wall (see figure 2074-E1).

AXIAL LEAD, TRANSPARENT BODY, POINT CONTACT

\* FIGURE 2074-E1. Whisker touches glass body wall (reject).

# APPENDIX E

b. Whisker loops touch one another (see figure 2074-E2 ).

\*FIGURE 2074-E2 . Whisker loops touch one another (reject).

c. Whisker angle over 10 degrees from normal (see figure 2074-E3 ).

\*FIGURE 2074-E3. Whisker angle over 10 degrees from normal (reject).

### APPENDIX E

E.1.7 <u>Whisker weld to post</u>. Any device that exhibits weld splash or splatter (tear dropped or balled) between whisker and post shall be rejected when it exceeds 25 percent of nominal lead diameter. The profile of whisker weld to the post shall not allow light penetration by more than 50 percent of lead diameter when using back lighting techniques.

E.1.8 <u>Solder voids</u>. A device shall be rejected if solder flow is less than 50 percent of the perimeter of the minimum available contact area of the die.

E.1.9 <u>Die to post contact area</u>. Solder shall be smoothly formed from one element to another and shall be fused to a minimum of one-half the available bonding area. Any solder overflow that touches the opposite surface of the die shall be cause for rejection.

E.1.10 <u>Die alignment</u>. A device shall be rejected if the die surface is not within 15° of being normal to the centerline of the mounting post.

E.1.11 Lead alignment defects (applicable to that portion of each lead within the glass envelope). A device whose lead is either misaligned or bent so that is makes an angle with the principle device axis greater than 10° shall be rejected.

E.12 <u>Die touches glass package (see figure 2074-E4</u>). A device shall be rejected if the die touches the glass envelope.

\* FIGURE 2074-E4. Die touches glass package (reject).

# APPENDIX F

# POWER RECTIFIERS AND REGULATORS

### F.1 Axial lead double plug opaque body.

F.1.1 <u>Die mounting and alignment</u>. After bonding die to the heat sink, plugs, or leads, the following shall be inspected for defects:

- a. Die geometry. A die shall be rejected if it is chipped or broken to the extent that 75 percent or less of the original surface remains.

- b. Axial alignment of plugs and die. Plugs shall be aligned axially within one-eighth of the diameter of either plug.

- c. Tilted die. A device shall be rejected if the die is tilted so that the die surface is greater than 5 degrees from being perpendicular to the mounting post axis.

F.1.2 <u>Die cracks</u>. Any die exhibiting cracks that reduce the total die area (or cracks extending into or across the junction area) to less than 75 percent of its original area shall be cause for rejection.

F.1.3 <u>Inadequate brazing</u>. A device shall be rejected if less than 90 percent of the visible metallized surface (perimeter) is brazed to the heat sink or lead.

F.1.4 <u>Flaking or loose material</u>. No unattached solder, braze, or other bonding material shall extend from the plugs. Any blistering or peeling of plug surface shall be cause for rejection.

F.1.5 <u>Extraneous matter</u>. A device shall be rejected if there is any extraneous, particulate matter between the terminal plugs or on the plug surface. No foreign stains shall be permitted on plug surfaces.

# APPENDIX G

# SMALL SIGNAL, COMPUTER, REGULATOR, LOW POWER RECTIFIERS, AND MICROWAVE DIODES

- G.1. Axial lead, metal body, solder contact design.

- \* G.1.1 Examinations before capping.

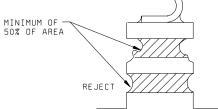

- \*a. Solder defects (see figures 2074-G1 and 2074-G2). Any device with a solder protrusion that extends more than twice the smallest protrusion width shall be rejected. Solder shall be smoothly formed from one element to another and shall be fused to a minimum of 50 percent of the perimeter between adjacent elements.

FIGURE 2074-G2. Solder flow.

# APPENDIX G

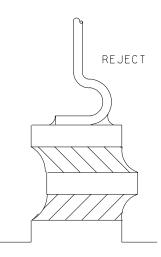

- \*b. Alignment (see figure 2074-G3). Any device whose element has its geometric center displaced more than 33 percent of its width from the die or die stack centerline shall be rejected.

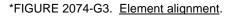

- \*c. Tilt (see figure 2074-G4). Any element of a device that is tilted more than 10 degrees from the mounting plane shall be cause for rejection.

\* FIGURE 2074-G4. Element tilt.

# APPENDIX G

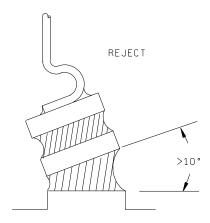

- \*d. Die chipouts (see figure 2074-G5). Any device die that exhibits chipouts extending more than 25 percent of the die width or to within 2 mils of the junction area shall be cause for rejection.

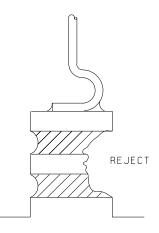

- \*e. Die cracks (see figure 2074-G6). Any die exhibiting cracks that reduce the total die area (or cracks extending into or across the junction area) to less than 75 percent of its original area shall be cause for rejection

\*FIGURE 2074-G5. Die chipout.

\*FIGURE 2074-G6. Die cracks.

f. Extraneous matter. A device shall be rejected if there are unattached solder balls, semiconductor material, chips, flaked plating, or opaque material that is larger than the smallest distance between exposed active areas.

# APPENDIX H

# POWER RECTIFIERS AND REGULATORS

H.1 Metal body stud mounted devices. The following inspections shall be made prior to capping.

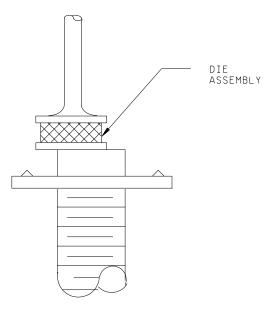

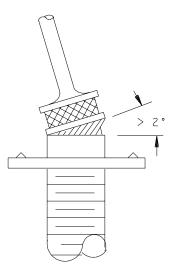

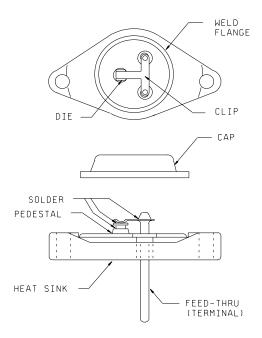

\* H.1.1 <u>Die and lead assembly (see figures 2074-H1 and 2074-H2)</u>. The die and lead assembly shall be located on the base pedestal so that there is complete contact over the design contact area. The lead shall be free of nicks and scrapes that reduce the lead diameter by more than 5 percent. The die and lead assembly shall not be tilted more than 5 degress with respect to the base.

DIE NOT CENTRALLY LOCATED

\* FIGURE 2074-H1. Offset die.

# APPENDIX H

TILTED DIE ASSEMBLY

\*FIGURE 2074-H2 . <u>Tilted die</u>.

# \* H.1.2 Extraneous matter.

- a. Solder slivers and spikes. A device shall be rejected if solder slivers and spikes are not securely attached to the parent body of the solder. A securely attached sliver or spike is one having a cross sectional area greater at the area of attachment than anywhere else on the solder protrusion and having no necked-down areas.